(Solved) : Compare Performance Twe Cache Deigs Bytc Addrossed Memery Sim Int Cache Design Disect Map Q30539529 . . .

![]()

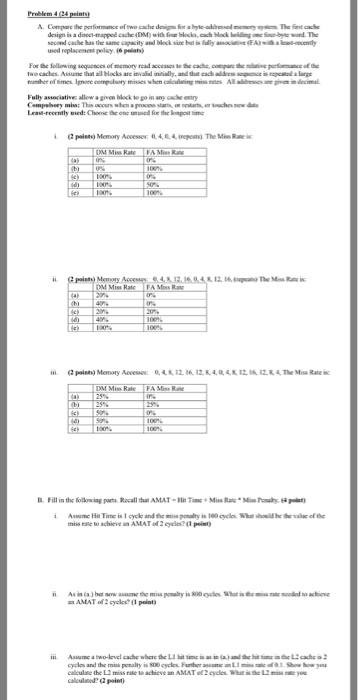

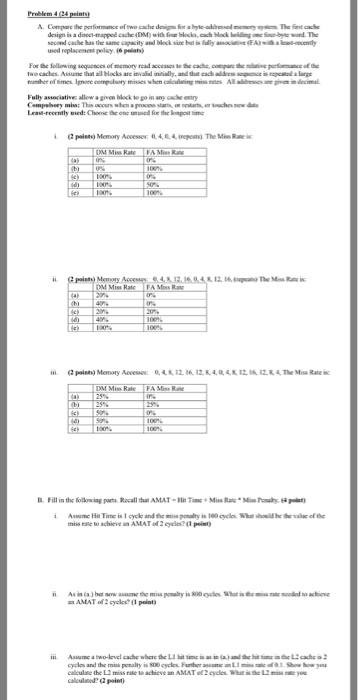

A. Compare the performance of twe cache deigs or a bytc-addrossed memery sim The int cache design is a disect-mapped cache (DM) with ou blocks, cach Nock elding on ouyodThe second cashe has the same capacity and bleck sine but is fully asocitive(F)a l-eniy used replacenest pelasy (6 peists For the Sollowing sequences of memory read accesses to the cache, conan the selative peremance of th two caches. Assume hat all locks are invalid intially, and that cach address soqence in rcaed a large numher of times Inore cempusory minses when calculaningis All aldheses ane indecimal Fully associative allow a given block to go in any cahe estry Lease-recently ?.cd: Chone the ene unnod fr kapal tme L (2 paiets) Memory Acesses: 04,0.4inegets) The Miss Rane is 4,8.12 poiets) Memory Aoesses: 0,4,8,12,16,12. 4,0,4, 12,16,12, 4.The Miss RareiK B. Fill in ths following parts Rocall thae AMAT-HnTimc Miss Rats Momaiy 6pit Assume Hia Time is 1 cycle and the miss pemality is 160 cycle Whhold be the valac of the miss eane to achieve an AMAT of2eyeles?( peint AMAT of2 cyclo? (1 point, cycles and the miss penaity is 900 cycles Further assume anLlie of1. Show how you caleulane the L2 miss rate le achieve an AMAT 2eycles Wh sthe L2you calculne? (2 point) Show transcribed image text

A. Compare the performance of twe cache deigs or a bytc-addrossed memery sim The int cache design is a disect-mapped cache (DM) with ou blocks, cach Nock elding on ouyodThe second cashe has the same capacity and bleck sine but is fully asocitive(F)a l-eniy used replacenest pelasy (6 peists For the Sollowing sequences of memory read accesses to the cache, conan the selative peremance of th two caches. Assume hat all locks are invalid intially, and that cach address soqence in rcaed a large numher of times Inore cempusory minses when calculaningis All aldheses ane indecimal Fully associative allow a given block to go in any cahe estry Lease-recently ?.cd: Chone the ene unnod fr kapal tme L (2 paiets) Memory Acesses: 04,0.4inegets) The Miss Rane is 4,8.12 poiets) Memory Aoesses: 0,4,8,12,16,12. 4,0,4, 12,16,12, 4.The Miss RareiK B. Fill in ths following parts Rocall thae AMAT-HnTimc Miss Rats Momaiy 6pit Assume Hia Time is 1 cycle and the miss pemality is 160 cycle Whhold be the valac of the miss eane to achieve an AMAT of2eyeles?( peint AMAT of2 cyclo? (1 point, cycles and the miss penaity is 900 cycles Further assume anLlie of1. Show how you caleulane the L2 miss rate le achieve an AMAT 2eycles Wh sthe L2you calculne? (2 point) Show transcribed image text

Expert Answer

Answer to Compare Performance Twe Cache Deigs Bytc Addrossed Memery Sim Int Cache Design Disect Map Q30539529 . . .

Related