Following Code Executed Processor 32 Architectural Registers Processor Able Issue Instruct Q43805795

The following code is to be executed on a processor with 32architectural registers. The processor is able to issueinstructions out-of-order. The processor is a single issue machine.The processor has different functional unit latencies with multiplyinstructions having a latency of 4 cycles, ALU operations having alatency of 1 cycles, and loads and stores having a latency of 2cycles. The processor stalls on WAW and WAR dependencies. Pretendthat you are the compiler and perform changes to the following codeto increase the performance of the code when executing on thisout-of-order processor. Assume that all registers not used are freeto be used by the compiler.

Which of the following code sequences would increase theperformance of the code on this OoO processor? Selectall that apply.

a)

b)

c)

d)

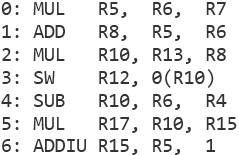

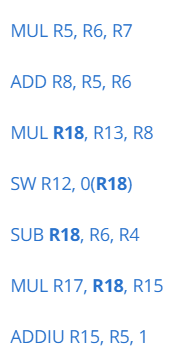

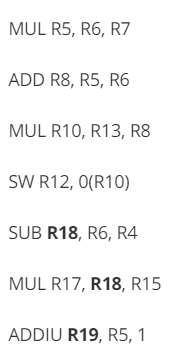

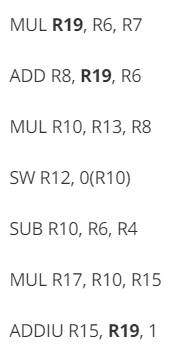

0: MUL R5, R6, R7 1: ADD R8, R5, R6 2: MUL R10, R13, R8 3: SW R12, (R10) 4: SUB R10, R6, R4 5: MUL R17, R10, R15 6: ADDIU R15, R5, 1 MUL RS, R6, R7 ADD R8, RS, R6 MUL R18, R13, R8 SW R12, 0(R18) SUB R10, RO, R4 MUL R17, R10, R15 ADDIU R19, R5, 1 MUL R5, R6, R7 ADD R8, R5, R6 MUL R18, R13, R8 SW R12, 0(R18) SUB R18, R6, R4 MUL R17, R18, R15 ADDIU R15, R5, 1 MUL R5, R6, R7 ADD R8, R5, R6 MUL R10, R13, R8 SW R12, 0(R10) SUB R18, R6, R4 MUL R17, R18, R15 ADDIU R19, R5, 1 MUL R19, R6, R7 ADD R8, R19, RO MUL R10, R13, R8 SW R12, 0(R10) SUB R10, R6, R4 MUL R17, R10, R15 ADDIU R15, R19,1 Show transcribed image text 0: MUL R5, R6, R7 1: ADD R8, R5, R6 2: MUL R10, R13, R8 3: SW R12, (R10) 4: SUB R10, R6, R4 5: MUL R17, R10, R15 6: ADDIU R15, R5, 1

MUL RS, R6, R7 ADD R8, RS, R6 MUL R18, R13, R8 SW R12, 0(R18) SUB R10, RO, R4 MUL R17, R10, R15 ADDIU R19, R5, 1

MUL R5, R6, R7 ADD R8, R5, R6 MUL R18, R13, R8 SW R12, 0(R18) SUB R18, R6, R4 MUL R17, R18, R15 ADDIU R15, R5, 1

MUL R5, R6, R7 ADD R8, R5, R6 MUL R10, R13, R8 SW R12, 0(R10) SUB R18, R6, R4 MUL R17, R18, R15 ADDIU R19, R5, 1

MUL R19, R6, R7 ADD R8, R19, RO MUL R10, R13, R8 SW R12, 0(R10) SUB R10, R6, R4 MUL R17, R10, R15 ADDIU R15, R19,1

Expert Answer

Answer to The following code is to be executed on a processor with 32 architectural registers. The processor is able to issue inst…

OR