1 5 Pt Cpu Clock 24ghz Half Clock Cycle Fetching Half Execution Access Time Primary Stora Q43859613

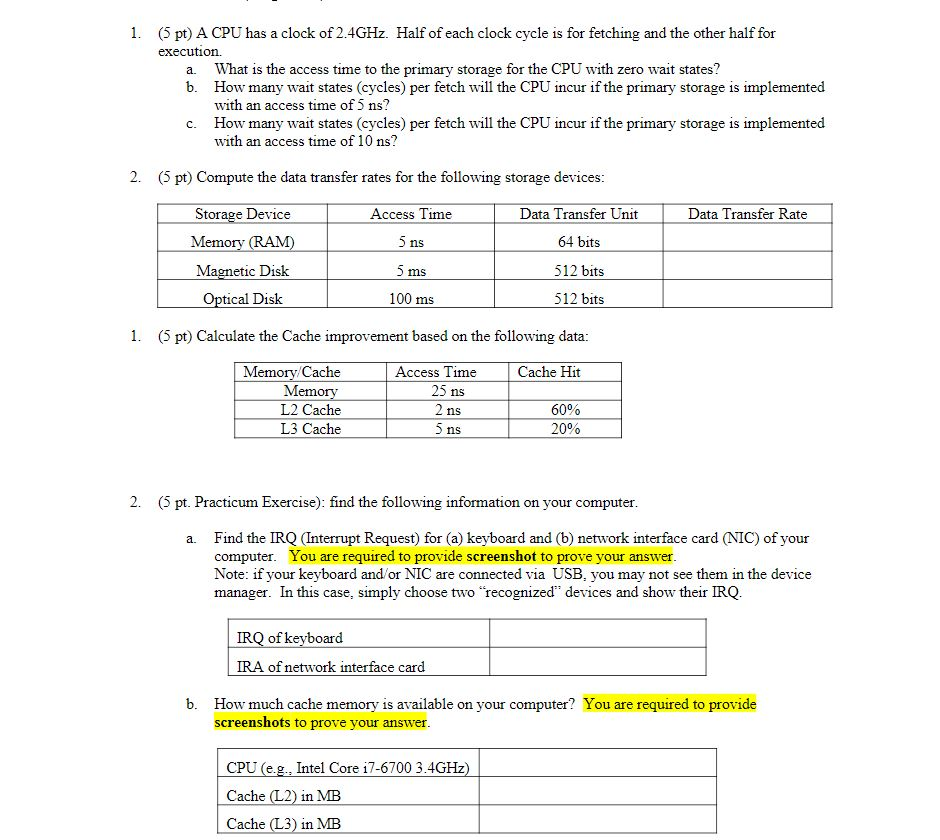

1. (5 pt) A CPU has a clock of 2.4GHz. Half of each clock cycle is for fetching and the other half for execution. a. What is the access time to the primary storage for the CPU with zero wait states? b. How many wait states (cycles) per fetch will the CPU incur if the primary storage is implemented with an access time of 5 ns? c. How many wait states (cycles) per fetch will the CPU incur if the primary storage is implemented with an access time of 10 ns? 2. (5 pt) Compute the data transfer rates for the following storage devices: Access Time I Data Transfer Rate Data Transfer Unit 64 bits 5 ns Storage Device Memory (RAM) Magnetic Disk Optical Disk 512 bits 5 ms 100 ms 512 bits 1. (pt) Calculate the Cache improvement based on the following data: Cache Hit Memory Cache Memory L2 Cache L3 Cache Access Time 25 ns 2 ns 5ns 60% 20% I 2. (5 pt. Practicum Exercise): find the following information on your computer. a Find the IRO (Interrupt Request) for (a) keyboard and (b) network interface card (NIC) of your computer. You are required to provide screenshot to prove your answer. Note: if your keyboard and/or NIC are connected via USB, you may not see them in the device manager. In this case, simply choose two “recognized” devices and show their IRQ. IRQ of keyboard IRA of network interface card b. How much cache memory is available on your computer? You are required to provide screenshots to prove your answer. CPU (e.g., Intel Core i7-6700 3.4GHz) Cache (L2) in MB Cache (L3) in MB Show transcribed image text 1. (5 pt) A CPU has a clock of 2.4GHz. Half of each clock cycle is for fetching and the other half for execution. a. What is the access time to the primary storage for the CPU with zero wait states? b. How many wait states (cycles) per fetch will the CPU incur if the primary storage is implemented with an access time of 5 ns? c. How many wait states (cycles) per fetch will the CPU incur if the primary storage is implemented with an access time of 10 ns? 2. (5 pt) Compute the data transfer rates for the following storage devices: Access Time I Data Transfer Rate Data Transfer Unit 64 bits 5 ns Storage Device Memory (RAM) Magnetic Disk Optical Disk 512 bits 5 ms 100 ms 512 bits 1. (pt) Calculate the Cache improvement based on the following data: Cache Hit Memory Cache Memory L2 Cache L3 Cache Access Time 25 ns 2 ns 5ns 60% 20% I 2. (5 pt. Practicum Exercise): find the following information on your computer. a Find the IRO (Interrupt Request) for (a) keyboard and (b) network interface card (NIC) of your computer. You are required to provide screenshot to prove your answer. Note: if your keyboard and/or NIC are connected via USB, you may not see them in the device manager. In this case, simply choose two “recognized” devices and show their IRQ. IRQ of keyboard IRA of network interface card b. How much cache memory is available on your computer? You are required to provide screenshots to prove your answer. CPU (e.g., Intel Core i7-6700 3.4GHz) Cache (L2) in MB Cache (L3) in MB

Expert Answer

Answer to 1. (5 pt) A CPU has a clock of 2.4GHz. Half of each clock cycle is for fetching and the other half for execution. a. Wha…

OR